# **HDL Coder™**

**Getting Started Guide**

# MATLAB® SIMULINK®

# **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

T

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

HDL Coder™ Getting Started Guide

© COPYRIGHT 2012-2019 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### **Patents**

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| March 2012     | Online only | New for Version 3.0 (Release 2012a)      |

|----------------|-------------|------------------------------------------|

| September 2012 | Online only | Revised for Version 3.1 (Release 2012b)  |

| March 2013     | Online only | Revised for Version 3.2 (Release 2013a)  |

| September 2013 | Online only | Revised for Version 3.3 (Release 2013b)  |

| March 2014     | Online only | Revised for Version 3.4 (Release 2014a)  |

| October 2014   | Online only | Revised for Version 3.5 (Release 2014b)  |

| March 2015     | Online only | Revised for Version 3.6 (Release 2015a)  |

| September 2015 | Online only | Revised for Version 3.7 (Release 2015b)  |

| October 2015   | Online only | Rereleased for Version 3.6.1 (Release    |

|                |             | 2015aSP1)                                |

| March 2016     | Online only | Revised for Version 3.8 (Release 2016a)  |

| September 2016 | Online only | Revised for Version 3.9 (Release 2016b)  |

| March 2017     | Online only | Revised for Version 3.10 (Release 2017a) |

| September 2017 | Online only | Revised for Version 3.11 (Release 2017b) |

| March 2018     | Online only | Revised for Version 3.12 (Release 2018a) |

| September 2018 | Online only | Revised for Version 3.13 (Release 2018b) |

| March 2019     | Online only | Revised for Version 3.14 (Release 2019a) |

| September 2019 | Online only | Revised for Version 3.15 (Release 2019b) |

|                |             |                                          |

# Contents

|    | About HDL Co                                                                                                                                                                                                  | oder                                   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| L  |                                                                                                                                                                                                               |                                        |

| ]  | HDL Coder Product Description                                                                                                                                                                                 | 1-2<br>1-2                             |

| \$ | Third-Party Synthesis Tools and Version Support FPGA-in-the-Loop Hardware Simulink Real-Time FPGA I/O: Speedgoat Target Hardware Generic ASIC/FPGA Hardware IP Core Generation Hardware FPGA Turnkey Hardware | 1-3<br>1-3<br>1-4<br>1-4<br>1-5<br>1-6 |

| •  | WHDL and Verilog Language Support                                                                                                                                                                             | 1-8                                    |

| ]  | HDL Coder Supported Hardware                                                                                                                                                                                  | 1-9                                    |

|    | Getting Started with HDL Co                                                                                                                                                                                   | oder                                   |

| -  | Synthesis Tool Path Setup                                                                                                                                                                                     | 2-2<br>2-2<br>2-3<br>2-4               |

| HDL Code Generation and FPGA Synthesis from a MATLAB Algorithm                                                                                                                                  | 3-2                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| About the Algorithm in This Example                                                                                                                                                             | 3-2<br>3-3<br>3-3<br>3-4<br>3-6                      |

| Generate HDL Code                                                                                                                                                                               | 3-7<br>3-9<br>3-9<br>3-9                             |

| Create Simulink Model for HDL Code Generation  Open Model and HDL Coder Library  Develop Design and Test Bench  Simulate and Verify Functionality of Design  Check Model for HDL Compatibility  | 3-11<br>3-14<br>3-16<br>3-17                         |

| Check HDL Compatibility of Model Using HDL Model Checker                                                                                                                                        |                                                      |

| Simple Up Counter Model Open the HDL Model Checker How to Run Checks In the HDL Model Checker Run Checks for Counter Model Fix HDL Model Checker Warnings or Failures Caveats Generate HDL Code | 3-19<br>3-20<br>3-21<br>3-22<br>3-23<br>3-25<br>3-26 |

| Generate HDL Code from Simulink Model Simple Up Counter Model Generate HDL Code View HDL Code Generation Files Verify Generated HDL Code                                                        | 3-27<br>3-27<br>3-28<br>3-30<br>3-30                 |

| Verify Generated Code from Simulink Model Using HDL Test Bench Simple Up Counter Model How to Verify the Generated Code                                                                         | 3-32<br>3-32<br>3-33                                 |

|     | What is a HDL Test Bench?                           |

|-----|-----------------------------------------------------|

|     | Generate HDL Test Bench                             |

|     | View HDL Test Bench Files                           |

|     | Run Simulation and Verify Generated HDL Code        |

|     | Deploy Generated HDL Code on Target Device          |

|     |                                                     |

| HDI | L Code Generation and FPGA Synthesis Using Simulink |

| Η   | DL Workflow Advisor                                 |

|     | Simple Up Counter Model                             |

|     | About HDL Workflow Advisor                          |

|     | Set Up Tool Path                                    |

|     | Open the HDL Workflow Advisor                       |

|     | Generate HDL Code                                   |

|     | Perform FPGA Synthesis and Analysis                 |

|     | Run Workflow at Command Line with a Script          |

# **About HDL Coder**

- "HDL Coder Product Description" on page 1-2

- "Supported Third-Party Tools and Hardware" on page 1-3

- "VHDL and Verilog Language Support" on page 1-8

- "HDL Coder Supported Hardware" on page 1-9

# **HDL Coder Product Description**

#### Generate VHDL and Verilog code for FPGA and ASIC designs

HDL Coder generates portable, synthesizable VHDL® and Verilog® code from MATLAB® functions, Simulink® models, and Stateflow® charts. The generated HDL code can be used for FPGA programming or ASIC prototyping and design.

HDL Coder provides a workflow advisor that automates the programming of Xilinx®, Microsemi®, and Intel® FPGAs. You can control HDL architecture and implementation, highlight critical paths, and generate hardware resource utilization estimates. HDL Coder provides traceability between your Simulink model and the generated Verilog and VHDL code, enabling code verification for high-integrity applications adhering to DO-254 and other standards.

# **Key Features**

- Target-independent, synthesizable VHDL and Verilog code

- Code generation support for MATLAB functions, System objects and Simulink blocks

- Mealy and Moore finite-state machines and control logic implementations using Stateflow

- Workflow advisor for programming Xilinx, Microsemi, and Intel application boards

- · Resource sharing and retiming for area-speed tradeoffs

- Code-to-model and model-to-code traceability for DO-254

- Legacy code integration

# **Supported Third-Party Tools and Hardware**

#### In this section...

"Third-Party Synthesis Tools and Version Support" on page 1-3

"FPGA-in-the-Loop Hardware" on page 1-3

"Simulink Real-Time FPGA I/O: Speedgoat Target Hardware" on page 1-4

"Generic ASIC/FPGA Hardware" on page 1-4

"IP Core Generation Hardware" on page 1-5

"FPGA Turnkey Hardware" on page 1-6

# **Third-Party Synthesis Tools and Version Support**

The HDL Workflow Advisor is tested with the following third-party FPGA synthesis tools:

- Intel Quartus Prime 18.1

- Xilinx Vivado® Design Suite 2018.3

- Microsemi Libero<sup>®</sup> SoC 11.8

- Xilinx ISE 14.7

To use third-party synthesis tools with HDL Coder, a supported synthesis tool must be installed, and the synthesis tool executable must be on the system path. For details, see "Tool Setup" on page 2-2.

## **FPGA-in-the-Loop Hardware**

The FPGAs supported for FPGA-in-the-loop simulation with HDL Verifier  $^{\text{\tiny TM}}$  are listed in the HDL Verifier documentation.

You can also add custom FPGA boards using the FPGA Board Manager. See "FPGA Board Customization" for details.

For FPGA-in-the-Loop or Customization for USRP® Device using the HDL Workflow Advisor, a supported synthesis tool must be installed, and the synthesis tool executable must be on the system path. For details, see "Tool Setup" on page 2-2.

# Simulink Real-Time FPGA I/O: Speedgoat Target Hardware

| Speedgoat<br>I/O Module | FPGA<br>Device              | Synthesis Tool                                                                                                    |

|-------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------|

| IO342                   | Xilinx Kintex<br>UltraScale | For more information and to learn about the synthesis tool requirements, see Xilinx HDL Support with Speedgoat IO |

| IO333, IO334,<br>IO335  | Xilinx<br>Kintex-7          | Modules.                                                                                                          |

| IO332, IO397            | Xilinx Artix-7              |                                                                                                                   |

| IO323, IO331            | Xilinx<br>Spartan-6         |                                                                                                                   |

# **Generic ASIC/FPGA Hardware**

The following hardware is supported for the Generic ASIC/FPGA workflow:

| Synthesis Tool | Device Family      |

|----------------|--------------------|

| Xilinx Vivado  | Kintex7            |

|                | Artix7             |

|                | Kintex UltraScale+ |

|                | KintexU            |

|                | Spartan7           |

|                | Virtex UltraScale+ |

|                | Virtex7            |

|                | VirtexU            |

|                | Zynq               |

|                | Zynq UltraScale+   |

| Xilinx ISE     | Virtex6            |

|                | Virtex5            |

|                | Virtex4            |

|                | Spartan-3A DSP     |

|                | Spartan 3E         |

| Synthesis Tool       | Device Family       |

|----------------------|---------------------|

|                      | Spartan3            |

|                      | Spartan6            |

| Altera® Quartus II   | Cyclone® III        |

|                      | Cyclone IV          |

|                      | Arria® II GX and GZ |

|                      | Stratix® IV         |

|                      | Stratix V           |

|                      | Cyclone III         |

|                      | Arria 10            |

|                      | Arria V GX          |

|                      | MAX 10              |

| Microsemi Libero SoC | SmartFusion2 SoC    |

|                      | RTG4                |

|                      | IGLOO2              |

# **IP Core Generation Hardware**

The following hardware is supported for the IP Core Generation workflow:

| Synthesis Tool | Target Platform                                            |

|----------------|------------------------------------------------------------|

| Xilinx Vivado  | ZedBoard and with FMC-HDMI-CAM and FMCOMMS2/3/4/           |

|                | ZC706 and with FMC-HDMI-CAM and FMCOMMS2/3/4/ and FMCOMMS5 |

|                | ZC702 with FMC-HDMI-CAM                                    |

|                | Zynq ZC706 evaluation kit                                  |

|                | Zynq ZC702 evaluation kit                                  |

|                | PicoZed FMC-HDMI-CAM                                       |

|                | Zynq UltraScale+ MPSoC ZCU102<br>Evaluation Kit            |

| Synthesis Tool    | Target Platform                                 |

|-------------------|-------------------------------------------------|

| Altera Quartus II | Arria 10 SoC development kit                    |

|                   | Cyclone V SoC development kit Rev. C and Rev. D |

|                   | Arrow DECA Max 10 FPGA development board        |

|                   | Arrow SoCKit development board                  |

|                   | Arria 10 GX FPGA development kit                |

# **FPGA Turnkey Hardware**

The following hardware is supported for the FPGA Turnkey workflow:

- Altera Arria II GX FPGA development kit

- · Altera Cyclone III FPGA development kit

- · Altera Cyclone IV GX FPGA development kit

- Altera DE2-115 development and education board

- XUP Atlys Spartan-6 development board

- Xilinx Spartan-3A DSP 1800A development board

- Xilinx Spartan-6 SP605 development board

- Xilinx Virtex-4 ML401 development board

- Xilinx Virtex-4 ML402 development board

- Xilinx Virtex-5 ML506 development board

- Xilinx Virtex-6 ML605 development board

For FPGA development boards that have more than one FPGA device, only one such device can be used with FPGA Turnkey.

## Supported FPGA Device Families for Board Customization

You can also add custom FPGA boards using the FPGA Board Manager. HDL Coder supports the following FPGA device families for board customization; that is, when you create your own board definition file. See "FPGA Board Customization" (HDL Verifier).

| Device Family |                          |

|---------------|--------------------------|

| Xilinx        | Kintex7                  |

|               | Spartan-3A DSP           |

|               | Spartan3                 |

|               | Spartan3A and Spartan3AN |

|               | Spartan3E                |

|               | Spartan6                 |

|               | Virtex4                  |

|               | Virtex5                  |

|               | Virtex6                  |

|               | Virtex7                  |

| Altera        | Cyclone III              |

|               | Cyclone IV               |

|               | Arria II                 |

|               | Stratix IV               |

|               | Stratix V                |

# **See Also**

# **More About**

• "Tool Setup" on page 2-2

# **VHDL** and **Verilog Language Support**

The generated HDL code complies with the following standards:

- VHDL-1993 (IEEE® 1076-1993) or later

- Verilog-2001 (IEEE 1364-2001) or later

# **HDL Coder Supported Hardware**

As of this release, HDL Coder supports the following hardware.

| Support Package      | Vendor | Earliest Release<br>Available | Last Release<br>Available |

|----------------------|--------|-------------------------------|---------------------------|

| Intel FPGA Boards    | Intel  | R2013b                        | Current                   |

| Intel SoC Devices    | Intel  | R2014b                        | Current                   |

| Xilinx FPGA Boards   | Xilinx | R2013b                        | Current                   |

| Xilinx Zynq Platform | Xilinx | R2013a                        | Current                   |

For a complete list of support packages, see Hardware Support.

In addition to these packages, HDL Coder includes built-in support for:

- FPGA-in-the-loop simulation with HDL Verifier

- Simulink Real-Time™ FPGA I/O hardware

- Custom FPGA boards using the FPGA Board Manager

For details, see "Supported Third-Party Tools and Hardware" on page 1-3.

# **Getting Started with HDL Coder**

# **Tool Setup**

#### In this section...

"Synthesis Tool Path Setup" on page 2-2

"HDL Simulator Setup" on page 2-3

"Xilinx System Generator Setup for ModelSim Simulation" on page 2-4

"Altera DSP Builder Setup" on page 2-5

"FPGA Simulation Library Setup" on page 2-5

"C/C++ Compiler Setup" on page 2-6

# **Synthesis Tool Path Setup**

- "hdlsetuptoolpath Function" on page 2-2

- "Add Synthesis Tool for Current HDL Workflow Advisor Session" on page 2-2

- "Check Your Synthesis Tool Setup" on page 2-3

- "Supported Tool Versions" on page 2-3

### hdlsetuptoolpath Function

To use HDL Coder with one of the supported third-party FPGA synthesis tools, add the tool to your system path using the hdlsetuptoolpath function. Add the tool to your system path before opening the HDL Workflow Advisor. If you already have the HDL Workflow Advisor open, see "Add Synthesis Tool for Current HDL Workflow Advisor Session" on page 2-2.

### Add Synthesis Tool for Current HDL Workflow Advisor Session

#### Simulink to HDL Workflow

- 1 At the MATLAB command line, use the hdlsetuptoolpath function to add the synthesis tool.

- In the HDL Workflow Advisor, in the **Set Target > Set Target Device and Synthesis Tool** step, to the right of **Synthesis tool**, click **Refresh**.

The synthesis tool is now available.

#### **MATLAB to HDL Workflow**

- 1 At the MATLAB command line, use the hdlsetuptoolpath function to add the synthesis tool.

- In the HDL Workflow Advisor, in the **Select Code Generation Target** step, to the right of **Synthesis tool**, click **Refresh list**.

The synthesis tool is now available.

#### **Check Your Synthesis Tool Setup**

To check your Altera Quartus synthesis tool setup in MATLAB, try launching the tool with the following command:

!quartus

To check your Xilinx Vivado synthesis tool setup in MATLAB, try launching the tool with the following command:

!vivado

To check your Xilinx ISE synthesis tool setup in MATLAB, try launching the tool with the following command:

!ise

To check your Microsemi Libero SoC synthesis tool setup in MATLAB, try launching the tool with the following command:

!libero

#### **Supported Tool Versions**

For supported tool versions, see "Third-Party Synthesis Tools and Version Support" on page 1-3.

## **HDL Simulator Setup**

To open the HDL simulator from MATLAB, enter these commands:

#### MATLAB Command to Open HDL Simulator

| HDL Simulator              | Command to Open the Simulator |

|----------------------------|-------------------------------|

| Cadence Incisive®          | nclaunch                      |

| Mentor Graphics® ModelSim® | vsim                          |

For example, to open the Mentor Graphics ModelSim simulator, enter this command:

vsim('vsimdir','C:\Program Files\ModelSim\questasim\10.5c\win64\vsim.exe')

To learn more about how to set up ModelSim, Questa<sup>®</sup>, or Incisive<sup>®</sup> for HDL simulation, or for cosimulation with HDL Verifier, see "HDL Simulator Startup" (HDL Verifier).

#### Add Simulation Tool for Current HDL Workflow Advisor Session

#### **MATLAB to HDL Workflow**

- **1** Set up your simulation tool.

- In the HDL Workflow Advisor, in the **HDL Verification** > **Verify with HDL Test Bench** task, click **Refresh list**.

The simulation tool is now available.

# Xilinx System Generator Setup for ModelSim Simulation

To generate ModelSim simulation scripts for a design containing Xilinx System Generator blocks, you must:

- Have compiled Xilinx simulation libraries.

- Specify the path to your compiled libraries.

## **Required Libraries for Vivado and ISE**

To generate ModelSim simulation scripts, you must have the following compiled Xilinx simulation libraries for your EDA simulator and target language:

- unisim

- simprim

- xilinxcorelib

To learn how to compile these libraries, refer to the Xilinx documentation.

- For Vivado, see compile simlib.

- For ISE, see compxlib.

#### **Specify Path to Required Libraries**

Specify the path to your compiled Xilinx simulation libraries by setting the XilinxSimulatorLibPath parameter for your model.

For example, you can use hdlset param to set XilinxSimulatorLibPath:

```

libpath = '/apps/Xilinx_ISE/XilinxISE-13.4/Linux/ISE_DS/ISE/vhdl/

mti_se/6.6a/lin64/xilinxcorelib';

hdlset param (bdroot, 'XilinxSimulatorLibPath', libpath);

```

# **Altera DSP Builder Setup**

To generate code for a design containing both Altera DSP Builder and Simulink blocks, you must open MATLAB with Altera DSP Builder. For details, refer to the Altera DSP Builder documentation.

# **FPGA Simulation Library Setup**

To map your design to an Altera or a Xilinx FPGA simulator library:

- Use Xilinx LogiCORE® IP Floating-Point Operator v5.0 or Altera floating-point megafunction IP cores.

- Specify the compiled simulation library and the target language for your EDA simulator. Use XilinxCoreLib simulation library for Xilinx LogiCORE IP and the EDA simulation library compiler for Altera megafunction IP.

To learn how to compile this library, refer to the Xilinx compxlib documentation .

Specify the path to your compiled Altera or Xilinx simulation libraries. Altera provides

the simulation model files in \quartus\eda\sim\_lib folder. Set the

SimulationLibPath parameter for your DUT.

For example, you can use hdlset param to set SimulationLibPath:

```

myDUT = gcb;

libpath = '/apps/Xilinx_ISE/XilinxISE-13.4/Linux/ISE_DS/ISE/vhdl/

mti_se/6.6a/lin64/xilinxcorelib';

hdlset_param (myDUT, 'SimulationLibPath', libpath);

```

You can also specify the simulation library path from the **HDL Code Generation** > **Test Bench** pane in the Configuration Parameters dialog box.

# **C/C++ Compiler Setup**

HDL Coder locates and uses a supported installed compiler. For most platforms, a default compiler is supplied with MATLAB. For a list of supported compilers, see at https://www.mathworks.com/support/compilers/current release/.

# See Also

### **More About**

• "Third-Party Synthesis Tools and Version Support" on page 1-3

# **Tutorials**

- "HDL Code Generation and FPGA Synthesis from a MATLAB Algorithm" on page 3-2

- "Create Simulink Model for HDL Code Generation" on page 3-11

- "Check HDL Compatibility of Model Using HDL Model Checker" on page 3-19

- "Generate HDL Code from Simulink Model" on page 3-27

- "Verify Generated Code from Simulink Model Using HDL Test Bench" on page 3-32

- "HDL Code Generation and FPGA Synthesis Using Simulink HDL Workflow Advisor" on page 3-39

# HDL Code Generation and FPGA Synthesis from a MATLAB Algorithm

#### In this section...

"About the Algorithm in This Example" on page 3-2

"Create Local Copy of Design and Testbench Files" on page 3-3

"Set Up Synthesis Tool Path" on page 3-3

"Test the Original MATLAB Algorithm" on page 3-3

"Set Up a Project Using HDL Coder App" on page 3-4

"Open the HDL Coder Workflow Advisor" on page 3-6

"Create Fixed-Point Versions of the Algorithm and Test Bench" on page 3-7

"Generate HDL Code" on page 3-9

"Verify Generated HDL Code" on page 3-9

"FPGA Synthesis and Implementation" on page 3-9

HDL Coder can generate VHDL and Verilog code from MATLAB algorithms, Simulink models, and Stateflow charts. You can then verify that the generated code matches your original algorithm, and deploy it on the target hardware.

This example illustrates how you can use HDL Coder to generate and synthesize HDL code for a MATLAB algorithm that implements a simple filter.

# About the Algorithm in This Example

This tutorial uses these files:

• mlhdlc\_sfir.m — Simple filter function from which you generate HDL code. To see the MATLAB code for the FIR filter algorithm, at the command-line, enter:

```

edit('mlhdlc sfir')

```

mlhdlc\_sfir\_tb.m — Test bench that the HDL Coder project uses to simulate the

filter using a representative input range. To see the MATLAB code for the FIR filter

test bench, at the command-line, enter:

```

edit('mlhdlc_sfir_tb')

```

## **Create Local Copy of Design and Testbench Files**

Before you begin generating code, In the MATLAB path, navigate to a folder that is writable, and then create a working folder to store the design and test bench files.

1 In your current working folder, create a folder called filter sfir.

```

mkdir filter sfir;

```

2 Copy the tutorial files, mlhdlc sfir.m and mlhdlc sfir tb.m, to this folder.

```

mlhdlc_demo_dir = fullfile(matlabroot, 'toolbox', 'hdlcoder',...

'hdlcoderdemos', 'matlabhdlcoderdemos');

copyfile(fullfile(mlhdlc_demo_dir, 'mlhdlc_sfir.m'), 'filter_sfir');

copyfile(fullfile(mlhdlc_demo_dir, 'mlhdlc_sfir_tb.m'), 'filter_sfir');

```

# **Set Up Synthesis Tool Path**

If you want to synthesize the generated HDL code, before you use HDL Coder to generate code, set up your synthesis tool path. To set up the path to your synthesis tool, use the hdlsetuptoolpath function. For example, if your synthesis tool is Xilinx Vivado

To check your Xilinx Vivado synthesis tool setup, launch the tool with the following command:

#### !vivado

If you are using another Synthesis tool, to see how to set up the tool path and the right tool version to use, see "Synthesis Tool Path Setup" on page 2-2.

# Test the Original MATLAB Algorithm

To verify the functionality of your MATLAB algorithm, before generating HDL code, simulate your MATLAB design.

1 Make the filter\_sfir folder your working folder, for example:

```

cd filter sfir

```

**2** Run the test bench. At the MATLAB command line, enter:

```

mlhdlc_sfir_tb

```

The test bench runs and plots the input signal and the filtered output.

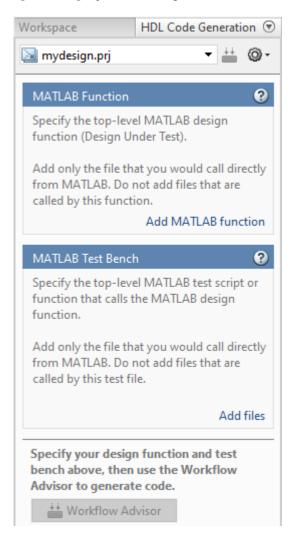

# Set Up a Project Using HDL Coder App

- 1 Open the **HDL Coder** App.

- To open the App from the UI, in MATLAB, on the **Apps** tab, in the **Code Generation** section, select **HDL Coder**. You can add this App to your favorites.

• To open the App from the command line, enter:

hdlcoder

**2** Specify the project name, for example, enter mydesign.

HDL Coder creates the project, mydesign.prj, in the local working folder, and opens the project in the right side of the MATLAB workspace.

- Add the design and test bench files. For **MATLAB Function**, add the mlhdlc\_sfir.m file, and for **MATLAB Test Bench**, add the mlhdlc\_sfir\_tb.m file.

- 4 To have the App automatically define the data types of the signals, when you add the MATLAB Function, select Autodefine types. Select the MATLAB Test Bench file mlhdlc\_sfir\_tb.m, and then run the test bench.

HDL Coder simulates the algorithm and test bench, and automatically defines input types. Select **Use these types**.

# **Open the HDL Coder Workflow Advisor**

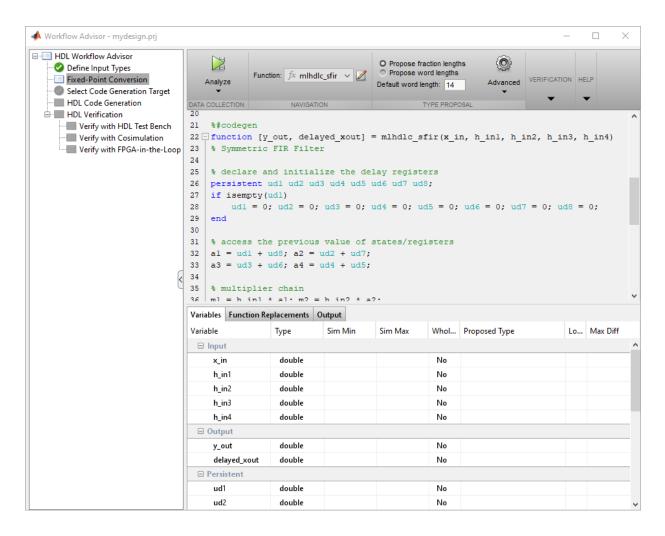

Use the HDL Coder Workflow Advisor to convert your algorithm to fixed-point, generate synthesizable HDL code, and then deploy the code to a target platform. To learn more about each individual task in the HDL Workflow Advisor, right-click that task, and select **What's This?**.

To open the Workflow Advisor, in the project, at the bottom of the pane, select the **Workflow Advisor** button. You see that the **Define Input Types** task has passed.

# Create Fixed-Point Versions of the Algorithm and Test Bench

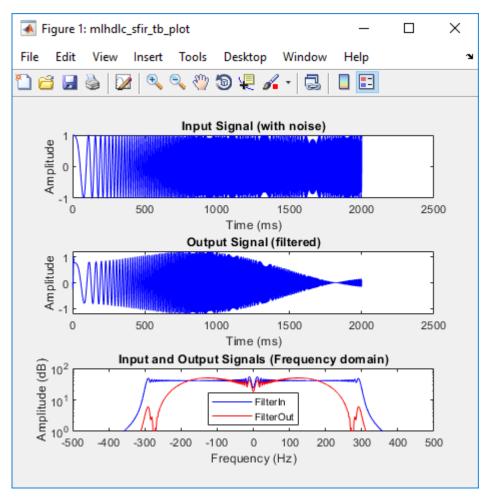

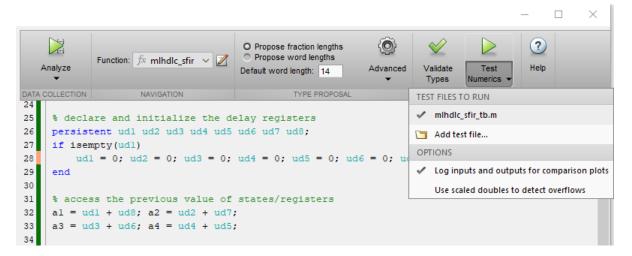

When you run fixed-point conversion, to propose fraction lengths for floating-point data types, HDL Coder uses the **Default word length**. In this tutorial, the **Default word length** is 14. The advisor provides a default **Safety Margin for Simulation Min/Max** of 0%. The advisor adjusts the range of the data by this safety factor. For example, a value of 4 specifies that you want a range of at least 4 percent larger.

Select the **Fixed-Point Conversion** task. The Fixed-Point Conversion tool opens in the right pane.

**1** At the top left, select **Analyze**.

After the simulation, HDL Coder displays the input signal, filtered output signal, and the frequency domain plot of input and output signals. If you navigate to **Fixed-Point Conversion** tool in the Workflow Advisor Window, you see that each input, output, and persistent variable has a **Sim Min**, **Sim Max**, and **Proposed Type** in the table.

This example uses the simulation ranges to infer fixed-point types. You can use **Compute Derived Ranges** to obtain the range using static range analysis. To learn more, see "Automated Fixed-Point Conversion".

2 At the top, in the Verification section, click **Validate Types**.

HDL Coder validates the build with the proposed fixed-point types and generates a fixed-point design.

At the top, in the Verification section, click the down-arrow for **Test Numerics** and select **Log inputs and outputs for comparison plots**. Click the top part of the **Test Numerics** button.

HDL Coder simulates the fixed-point design with the original test bench, compares the output to the original floating-point design output, and then displays the difference as an error signal.

4 In the bottom, you see a **Verification Output** tab. The tab displays a link to the report mlhdlc\_sfir\_fixed\_report.html. To explore the fixed-point code for the mlhdlc sfir function, open the report.

To see the fixed-point code in the MATLAB Editor, in the filter\_sfir folder, you see a codegen folder. When you navigate this folder, you see a mlhdlc\_sfir\_fixpt file. Open this file.

#### **Generate HDL Code**

- If you want to synthesize your design on a target FPGA platform, select the **Select Code Generation Target** task. Leave **Workflow** to **Generic ASIC/FPGA** and specify the **Synthesis tool**. If you don't see the synthesis tool, select **Refresh list**.

- 2 Before generating code, to customize code generation options, in the HDL Code Generation task, use the Target, Coding Style, Clocks and Ports, Optimizations, Advanced, and Script Options tabs

- **3** To generate HDL code, in the **HDL Code Generation** task, select **Run**.

The message window has a links to the generated HDL code and the resource report. Click the links to view the code and resource report.

# **Verify Generated HDL Code**

- In the HDL Workflow Advisor left pane, select HDL Verification > Verify with HDL Test Bench task.

- 2 Enable Generate HDL test bench and disable Skip this step. Enable Simulate generated HDL test bench and select a simulation tool. Click Run.

The task generates an HDL test bench, then simulates the fixed-point design using the selected simulation tool, and generates a compilation report and a simulation report.

# **FPGA Synthesis and Implementation**

Select Synthesis and Analysis and disable Skip this step. Run the Create Project task.

This task creates a synthesis project for the HDL code. HDL Coder uses this project in the next task to synthesize the design.

- 2 Select and run **Run Synthesis** task. This task:

- Launches the synthesis tool in the background.

- Opens the synthesis project created in the previous task, compiles HDL code, synthesizes the design, and emits netlists and related files.

- Generates a synthesis report.

- **3** Select and run **Run Implementation** task. This task:

- · Launches the synthesis tool in the background.

- Runs a Place and Route process that takes the circuit description produced by the previous mapping process, and emits a circuit description suitable for programming an FPGA.

- Emits pre- and post-routing timing information for use in critical path analysis and back annotation of your source model.

# See Also

## **Related Examples**

- "Basic HDL Code Generation with the Workflow Advisor"

- "Getting Started with MATLAB to HDL Workflow"

- "Generate HDL Code from MATLAB Code Using the Command Line Interface"

# **Create Simulink Model for HDL Code Generation**

#### In this section...

"Open Model and HDL Coder Library" on page 3-11

"Develop Design and Test Bench" on page 3-14

"Simulate and Verify Functionality of Design" on page 3-16

"Check Model for HDL Compatibility" on page 3-17

HDL Coder can generate VHDL and Verilog code from MATLAB code, Simulink models, and Stateflow charts. You can then verify that the generated code matches your original algorithm, and deploy it on the target hardware.

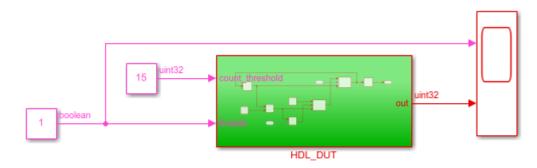

This example illustrates how you can create a Simulink model for HDL code generation. The model is a simple up counter algorithm that wraps back to zero after it reaches the upper limit that you specify.

# **Open Model and HDL Coder Library**

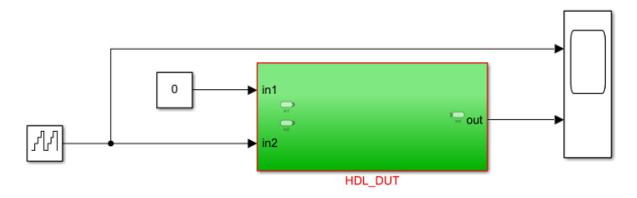

Start MATLAB. From the MATLAB toolstrip, click the **Simulink** button the **HDL Coder** section, select the **Blank DUT** template.

Selecting this template opens a Simulink model that is preconfigured for HDL code generation. Save the model with a file name such as hdlcoder simple up counter.slx in a working folder that is writable.

Note: This model is configured with 'hdlsetup'

Add your design targeted for ASIC/FPGA inside HDL\_DUT and then run the following command: makehdl('HDL\_DUT')

When you create a model for HDL code generation, you partition the model into a Design-Under-Test (DUT) and a test bench. The DUT is a Subsystem that is mostly at the top level of your model, and contains the algorithm for which you generate HDL code. Blocks outside this Subsystem form the test bench, and contains inputs to the Subsystem and output values that are logged. The test bench ensures that the DUT functionality is as expected.

For the test bench, you can use blocks that are not supported for HDL code generation. In the **Blank DUT** template, the model has a **HDL\_DUT** Subsystem that corresponds to the DUT. Blocks outside the **HDL\_DUT** Subsystem form the test bench.

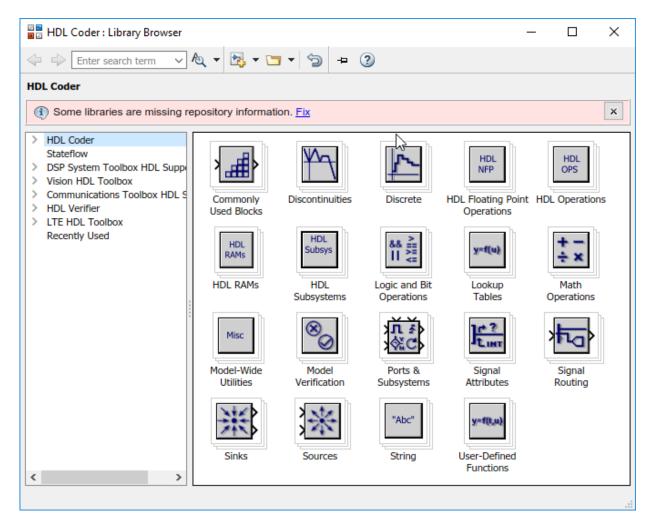

Open the HDL Coder Block Library for designing your counter algorithm. To filter the Simulink Library Browser to show block libraries that support HDL code generation, in the Apps tab, select HDL Coder. The HDL Code tab appears. Select HDL Block Properties > Open HDL Block Library.

In the **HDL Coder** library, you see several blocks that are pre-configured for HDL code generation. Blocks in this library are available with Simulink. If you do not have HDL Coder, you can simulate the blocks in your model, but cannot generate HDL code.

You can find additional HDL-supported blocks in these block libraries:

DSP System Toolbox HDL Support

- Communications Toolbox HDL Support

- Vision HDL Toolbox

- LTE HDL Toolbox

To restore the Library Browser to the default view, at the MATLAB command-line, enter:

hdllib('off')

**Note** The set of supported blocks tend to change each release. Rebuild your supported blocks library each time you install a new version of this product.

## **Develop Design and Test Bench**

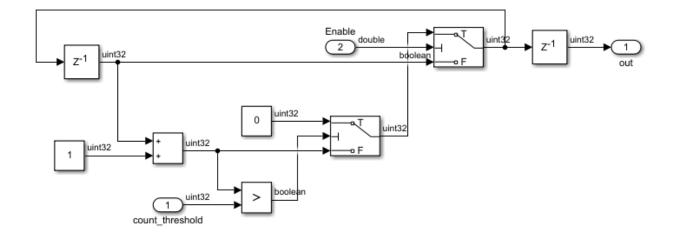

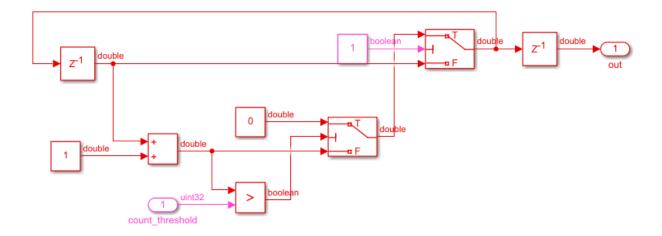

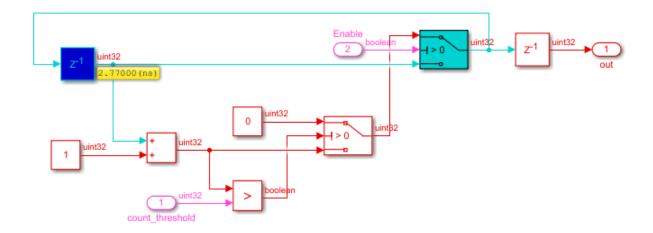

Double-click the **HDL\_DUT** Subsystem. Drag blocks from the **HDL Coder** library and add them to your model. This table illustrates the blocks to add to your model for designing the up counter. To learn about what a block does, and to specify the block parameters for that block, double-click the block.

| Block                  | Library                     | Number of<br>Blocks | Block Parameters                                          |

|------------------------|-----------------------------|---------------------|-----------------------------------------------------------|

| Constant               | Sources                     | 2                   | • Constant values: 1 and 0                                |

|                        |                             |                     | Output data type:     uint32                              |

| Switch                 | Signal Routing              | 2                   | Criteria for passing first<br>input: u2 > Threshold       |

| Delay                  | Discrete                    | 2                   | Delay length: 1                                           |

| Add                    | Math Operations             | 1                   | Accumulator data type:<br>Inherit: Same as first<br>input |

| Relational<br>Operator | Logic and Bit<br>Operations | 1                   | Relational operator: >                                    |

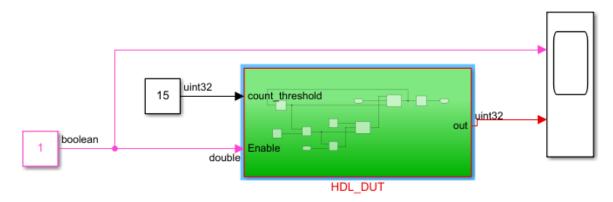

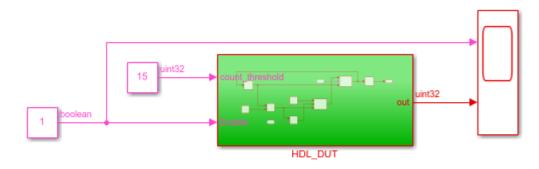

Rename the input ports In1 and In2 to count\_threshold and Enable respectively. Place the blocks in your model and connect them as shown in figure.

The Enable signal specifies whether the counter should count upwards from the previous value. When the Enable signal is logic high, the counter counts up from zero to the count\_threshold value. When the value of out becomes equal to the count\_threshold value, the counter wraps back to zero and starts counting again. When the Enable signal becomes logic low, the counter holds the previous value.

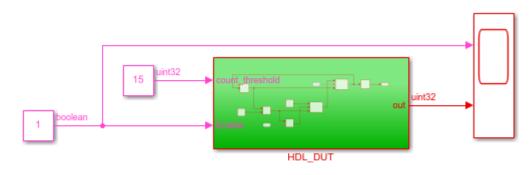

- **3** Navigate to the top level of the model and change the input settings.

- Constant block input to count\_threshold: This input decides the maximum value up to which the counter should count. This example illustrates how to design a 4-bit up counter. Therefore, set the **Constant value** to 15 (2^4 1), and set the **Output data type** to uint32.

**Note** Make sure that the output data type of this Constant block matches the output data type of the Constant blocks inside the **HDL DUT** Subsystem.

• Counter Free-Running block input to Enable: For this example, remove the Counter Free-Running block. Replace this block with a Constant block that has a value of 1 and **Output data type** set to boolean.

This figure shows the top level of your model after you have applied these settings.

Note: This model is configured with 'hdlsetup'

Add your design targeted for ASIC/FPGA inside HDL\_DUT and then run the following command: makehdl('HDL\_DUT')

To learn more about how to create a model, see "Create a Simple Model" (Simulink).

# Simulate and Verify Functionality of Design

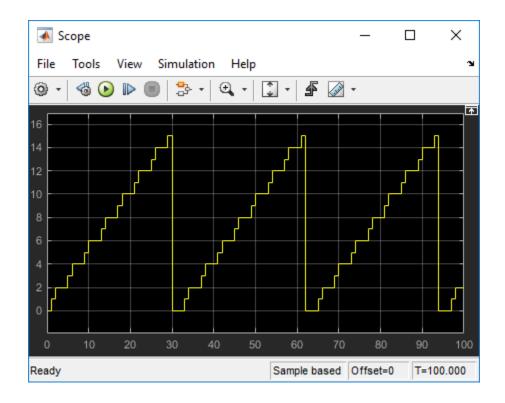

Simulate your model by pressing the button. To see the simulation results, open the Scope block at the top level of your model. The simulation results display the Enable signal at the top generating a constant value of 1 and the out signal counting from 0 to 15, then wrapping back to zero, and then counting up again. This figure displays the waveform of the output signal out.

# **Check Model for HDL Compatibility**

You have now simulated the model and verified the functionality of your design. Before you generate HDL code, you must verify that the model settings are compatible for HDL code generation. To make your design compatible for HDL code generation, you use the HDL Model Checker. To learn how to use the HDL Model Checker, see "Check HDL Compatibility of Model Using HDL Model Checker" on page 3-19.

## See Also

$checkhdl \mid hdllib \mid hdlmodelchecker \mid hdlsetup$

## **More About**

"Use Simulink Templates for HDL Code Generation"

- "Generate HDL Code from Simulink Model" on page 3-27

- "Verify Generated Code from Simulink Model Using HDL Test Bench" on page 3-32

- "HDL Code Generation and FPGA Synthesis Using Simulink HDL Workflow Advisor" on page 3-39

# Check HDL Compatibility of Model Using HDL Model Checker

#### In this section...

"Simple Up Counter Model" on page 3-19

"Open the HDL Model Checker" on page 3-20

"How to Run Checks In the HDL Model Checker" on page 3-21

"Run Checks for Counter Model" on page 3-22

"Fix HDL Model Checker Warnings or Failures" on page 3-23

"Caveats" on page 3-25

"Generate HDL Code" on page 3-26

Before you can generate HDL code, it is recommended that you verify the compatibility of your algorithm modeled in Simulink for HDL code generation. To verify model compatibility, you use the HDL Model Checker. The HDL Model Checker verifies and updates your Simulink model or subsystem for compatibility with HDL code generation. The Model Checker checks for model configuration settings, ports and subsystem settings, block settings, support for native floating point, and conformance to the industry-standard rules. The Model Checker produces a report that lists suboptimal conditions or settings, and then proposes better model configuration settings.

This example shows how you can update a simple up counter model for HDL compatibility. To learn more about the counter algorithm and how you can create this model, see "Create Simulink Model for HDL Code Generation" on page 3-11.

# **Simple Up Counter Model**

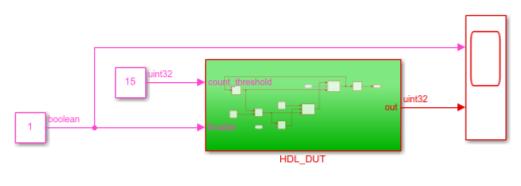

Open this model to see a simple up counter. The model counts up from zero to a threshold value and then wraps back to zero. In this model, the threshold value is set to 15. You can change the threshold value by changing the value of the Constant block that is input to the count\_threshold port. The Enable signal specifies whether the counter should count up or hold the previous value. The Enable signal is set to 1 which means that the counter counts upwards continuously.

```

open_system('hdlcoder_simple_up_counter.slx')

set_param('hdlcoder_simple_up_counter', 'SimulationCommand', 'Update')

```

Note: This model is configured with 'hdlsetup'

Add your design targeted for ASIC/FPGA inside HDL\_DUT and then run the following command: makehdl("HDL\_DUT")

## Open the HDL Model Checker

To open the HDL Model Checker, in the **Apps** tab, select **HDL Code**. The **HDL Code** tab appears. Select the DUT Subsystem and then click **HDL Code Advisor**.

**Note** You open the HDL Model Checker and then run checks for the DUT Subsystem that you want to generate code for. The top level model can contain blocks that are not compatible for HDL code generation. Running the HDL Model Checker for the entire model can flag these blocks and your model as incompatible for HDL code generation.

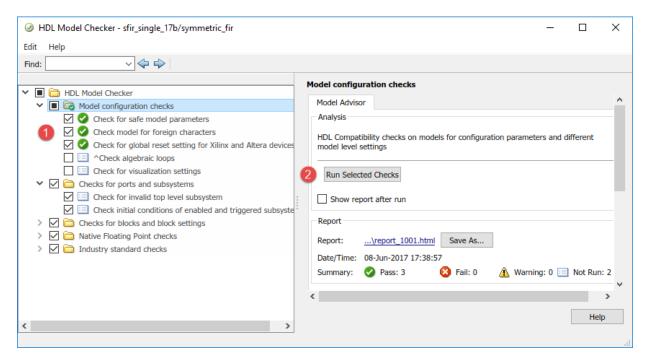

In the HDL Model Checker, the left pane lists the folders in the hierarchy. Each folder represents a group or category of related checks. Expanding the folders shows available checks in each folder. From the left pane, you can select a folder or an individual check. The HDL Model Checker displays information about the selected folder or check in the right pane. The content of the right pane depends on the selected folder or check. The right pane has a **Result** subpane that contains a display area for status messages and other task results.

To learn more about each individual check, right-click that check, and select **What's This?**.

## How to Run Checks In the HDL Model Checker

In the HDL Model Checker window, you can run individual checks or a group of checks. To run a check, **Select** that check and then click **Run This Check**. For example, to run the **Check for safe model parameters**, select the check box, and then click **Run This Check**.

In the HDL Model Checker window, you can run a group of checks within a folder.

- **1** Select the checks that you want to run.

- 2 Select the folder that contains these checks and then click **Run Selected Checks**.

This example shows how to run selected checks in the **Model configuration checks** folder.

## **Run Checks for Counter Model**

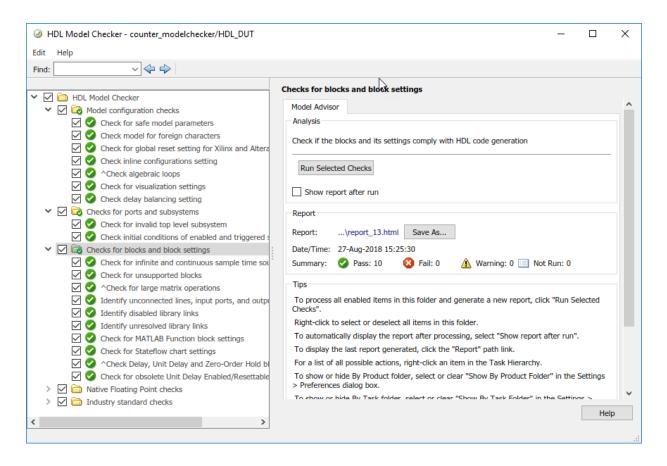

By using this approach, for your counter model, run all checks in these folders:

- Model Configuration checks

- Checks for ports and subsystems

- Checks for blocks and block settings

For this example, you do not need to run the checks in **Native Floating Point checks** and **Industry standard checks** folders. To learn more about these checks, see "Model Checks in HDL Coder".

For the counter model, the checks display the results as **Passed**, which means that the model is compatible for HDL code generation.

## **Fix HDL Model Checker Warnings or Failures**

In the HDL Model Checker, if a check fails, the right pane shows the warning or failure information in a **Result** subpane. The **Result** subpane displays model settings that are not compliant. For some tasks, use the **Action** subpane to apply the Model Checker recommended settings.

For example, inside the **HDL\_DUT** Subsystem, consider that you remove the **Enable** port and replace this port with a Constant input that has a value of 1.

Now, if you run the **Check for infinite and continuous sample time sources** check, the HDL Model Checker displays this warning.

To apply the correct model configuration settings that the code generator reported in the **Result** subpane, click the **Modify Settings** button. After you click **Modify Settings**, the **Result** subpane reports the changes that were applied. In this example, the **Sample time** of the Constant block is reset to -1. You can now run this check.

## **Caveats**

If you reference one model in another by using a Model block, the HDL Model Checker

checks the model configurations or settings of the parent model. To check whether the

referenced model is compatible with HDL code generation, open the HDL Model

Checker for the referenced model, and then run the checks.

- If you run the checks on masked library blocks in your Simulink model, the Model Checker cannot verify whether the blocks inside the library blocks have HDLcompatible settings.

- When you apply Model Advisor checks to your model, it increases the likelihood that

your model does not violate certain modeling standards or guidelines. However, it does

not guarantee that the design is ready for HDL code generation. Make sure that you

verify the design by using multiple methods for HDL code generation readiness.

### **Generate HDL Code**

The counter model is now compatible for HDL code generation. You can generate HDL code for the **HDL\_DUT** Subsystem, which contains the counter algorithm. To learn how to generate code, see "Generate HDL Code from Simulink Model" on page 3-27.

## See Also

checkhdl|hdlmodelchecker|hdlsetup

## **More About**

- "Model Checks in HDL Coder"

- "Verify Generated Code from Simulink Model Using HDL Test Bench" on page 3-32

- "HDL Code Generation and FPGA Synthesis Using Simulink HDL Workflow Advisor" on page 3-39

# **Generate HDL Code from Simulink Model**

#### In this section...

"Simple Up Counter Model" on page 3-27

"Generate HDL Code" on page 3-28

"View HDL Code Generation Files" on page 3-30

"Verify Generated HDL Code" on page 3-30

This example shows how you can generate HDL code for a simple Counter model. The model is a simple up counter that counts up from zero to a threshold value and then wraps back to zero. Before you generate HDL code for this model, it is recommended that you verify the HDL compatibility of your model by using the HDL Model Checker. To learn how to:

- Create this counter model, see "Create Simulink Model for HDL Code Generation" on page 3-11.

- Check HDL compatibility of the counter model, see "Check HDL Compatibility of Model Using HDL Model Checker" on page 3-19.

By default, HDL Coder creates an hdlsrc folder in the current working folder to generate the HDL files. Therefore, before you proceed to generate HDL code, make sure that your current working folder is writeable.

## **Simple Up Counter Model**

Open this model to see a simple up counter. The model counts up from zero to a threshold value and then wraps back to zero. In this model, the threshold value is set to 15. You can change the threshold value by changing the value of the Constant block that is input to the count\_threshold port. The Enable signal specifies whether the counter should count up or hold the previous value. The Enable signal is set to 1 which means that the counter counts upwards continuously.

```

open_system('hdlcoder_simple_up_counter.slx')

set param('hdlcoder simple up counter', 'SimulationCommand', 'Update')

```

Note: This model is configured with 'hdlsetup'

Add your design targeted for ASIC/FPGA inside HDL\_DUT and then run the following command: makehdl('HDL\_DUT')

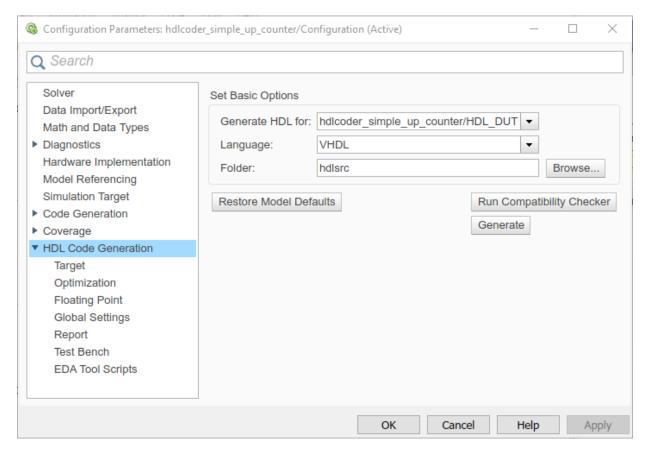

## **Generate HDL Code**

To generate code, you use the **HDL Code** tab in the To open the HDL Model Checker, Select the DUT Subsystem and then click **HDL Code Advisor**.

For the up counter model, the **HDL\_DUT** Subsystem is the DUT. To generate code for the DUT:

- $1 \quad \hbox{ In the $Apps$ tab, select $HDL$ $Coder$. The $HDL$ $Code$ tab appears. } \\$

- Select the DUT Subsystem in your model, and make sure that this Subsystem name appears in the **Code for** option. To remember the selection, you can pin this option. Click **Generate HDL Code**.

By default, HDL Coder generates VHDL code in the target hdlsrc folder.

If you want to generate Verilog code, you can specify this setting in the **HDL Code Generation** pane of the Configuration Parameters dialog box. Before you generate code, you can also customize model-level settings for your design such as enable native floating-point support, generate resource and traceability reports, use model-level optimizations, and modify other global settings.

To generate Verilog code for the counter model:

- 1 In the **HDL Code** tab, click **Settings**.

- In the **HDL Code Generation** pane, for **Language**, select Verilog. Leave other settings to the default. Click **Apply** and then click **Generate**.

HDL Coder compiles the model before generating code. Depending on model display options such as port data types, the model can change in appearance after code generation. As code generation proceeds, HDL Coder displays progress messages in the MATLAB command line with:

- Link to the Configuration Set that indicates the model for which the Configuration Parameters are applied.

- Links to the generated files. To view the files in the MATLAB Editor, click the links.

The process completes with the message:

### HDL Code Generation Complete.

## View HDL Code Generation Files

A folder icon for the hdlsrc folder is now visible in the Current Folder browser. To view generated code and script files, double-click the hdlsrc folder icon. In the folder, you see a file containing the VHDL or Verilog code, a script to compile the generated code, a synthesis script, and a mapping file. For example, if you generated code for the symmetric\_fir Subsystem, you see these files in the hdlsrc folder:

HDL\_DUT.vhd: This file is the VHDL code that contains the entity definition and RTL architecture implementing the up counter that you designed.

**Note** If you generated Verilog code, you get a HDL DUT. v file.

- HDL\_DUT\_compile.do: Mentor Graphics ModelSim compilation script. To invoke this script and compile the generated VHDL code, you use the vcom command.

- HDL\_DUT\_symplify.tcl: This file is a Symplify® synthesis TCL script.

- HDL\_DUT\_map.txt: This report file is a mapping file that generated entities or modules to the subsystems that generated them. See "Trace Code Using the Mapping File".

- HDL\_DUT\_report.html: This file is a HDL Code Generation Check report displays

the status of HDL code generation and any warnings or messages. If HDL code

generation fails, you see the cause of failure in the Check report.

- gm\_hdlcoder\_simple\_up\_counter.slx: This file is a generated model that behaviorally represents the HDL code in the Simulink modeling environment. For more information, see "Generated Model and Validation Model".

## **Verify Generated HDL Code**

Before you proceed to deploy your design on the target hardware, you must verify the generated HDL code. From the hdlsrc folder, navigate to the current working folder. To learn how you can verify the generated HDL code, see "Verify Generated Code from Simulink Model Using HDL Test Bench" on page 3-32.

# See Also

hdlset\_param|hdlsetup|makehdl

## **More About**

- "Create Simulink Model for HDL Code Generation" on page 3-11

- "HDL Code Generation and FPGA Synthesis Using Simulink HDL Workflow Advisor" on page 3-39

# Verify Generated Code from Simulink Model Using HDL Test Bench

#### In this section...

"Simple Up Counter Model" on page 3-32

"How to Verify the Generated Code" on page 3-33

"What is a HDL Test Bench?" on page 3-33

"Generate HDL Test Bench" on page 3-34

"View HDL Test Bench Files" on page 3-35

"Run Simulation and Verify Generated HDL Code" on page 3-36

"Deploy Generated HDL Code on Target Device" on page 3-37

This example shows how to generate a HDL test bench and verify the generated code for your design. The example assumes that you have already generated HDL code for your model. This example illustrates how to verify the generated code for a simple up counter. To learn more about this counter model and how to generate HDL code, see "Generate HDL Code from Simulink Model" on page 3-27.

**Note** If you haven't already generated HDL code, you can still open this model and generate the HDL test bench. Before generating the test bench, HDL Coder runs code generation to ensure that there is at least one successful code generation run before generating the testbench.

## **Simple Up Counter Model**

Open this model to see a simple up counter. The model counts up from zero to a threshold value and then wraps back to zero. In this model, the threshold value is set to 15. You can change the threshold value by changing the value of the Constant block that is input to the count\_threshold port. The Enable signal specifies whether the counter should count up or hold the previous value. The Enable signal is set to 1 which means that the counter counts upwards continuously.

```

open_system('hdlcoder_simple_up_counter.slx')

set_param('hdlcoder_simple_up_counter', 'SimulationCommand', 'Update')

```

Note: This model is configured with 'hdlsetup'

Ъ

Add your design targeted for ASIC/FPGA inside HDL\_DUT and then run the following command: makehdl('HDL\_DUT')

# **How to Verify the Generated Code**

This example illustrates how to generate a HDL test bench to simulate and verify the generated HDL code for your design. You can also verify the generated HDL code from your model using these methods:

| Verification Method                      | For More Information                   |  |

|------------------------------------------|----------------------------------------|--|

| Validation Model                         | "Generated Model and Validation Model" |  |

| HDL Cosimulation (requires HDL Verifier) | "Cosimulation"                         |  |

| SystemVerilog DPI Test Bench             | "SystemVerilog DPI Test Bench"         |  |

| FPGA-in-the-Loop                         | "FPGA-in-the-Loop"                     |  |

## What is a HDL Test Bench?

To verify the functionality of the HDL code that you generated for the DUT, generate a HDL test bench. A test bench includes:

- Stimulus data generated by signal sources connected to the entity under test.

- Output data generated by the entity under test. During a test bench run, this data is compared to the outputs of the VHDL model, for verification purposes.

- · Clock, reset, and clock enable inputs to drive the entity under test.

- A component instantiation of the entity under test.

- Code to drive the entity under test and compare its outputs to the expected data.

You can simulate the generated test bench and script files with the Mentor Graphics ModelSim simulator.

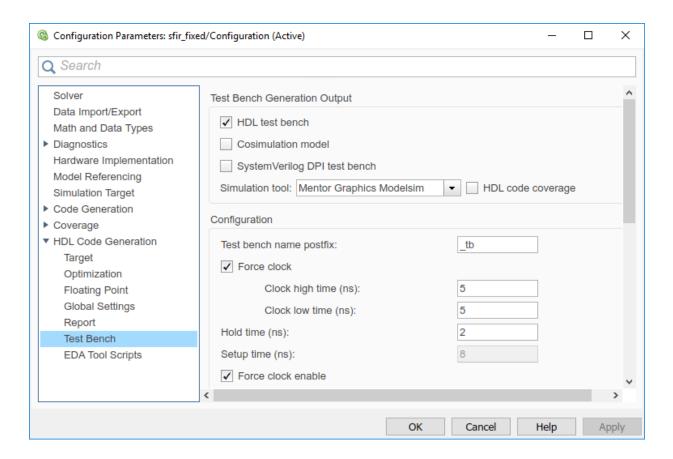

## **Generate HDL Test Bench**

Depending on whether you generated VHDL or Verilog code, generate VHDL or Verilog test bench code. The test bench code drives the HDL code that you generated for the DUT. By default, the HDL code and the test bench code are written to the same target folder hdlsrc relative to the current folder.

For the up counter model, the **HDL\_DUT** Subsystem is the DUT. To generate the testbench, select this Subsystem. You cannot generate a HDL testbench for an entire model.

- 1 In the **Apps** tab, select **HDL Coder**. The **HDL Code** tab appears.

- 2 Select the DUT Subsystem in your model, and make sure that this Subsystem name appears in the **Code for** option. To remember the selection, you can pin this option. Click **Generate Testbench**.

By default, HDL Coder generates VHDL testbench code in the target hdlsrc folder.

To generate Verilog testbench code for the counter model:

- 1 In the HDL Code tab, click Settings.

- 2 In the **HDL Code Generation** pane, for **Language**, select **Verilog**. Leave other settings to the default.

- 3 In the HDL Code Generation > Test Benchpane, click Generate Test Bench.

# **View HDL Test Bench Files**

1 If you haven't already generated code for your model, HDL Coder compiles the model and generates HDL code before generating the test bench. Depending on model display options such as port data types, the model can change in appearance after code generation.

As test bench generation proceeds, HDL Coder displays progress messages. The process should complete with the message

### HDL TestBench Generation Complete.

- After generating the test bench, you see the generated files in the hdlsrc folder. For example, if you generated a test bench for the HDL\_DUT Subsystem in your up counter model, the folder contains:

- HDL\_DUT\_tb.vhd: VHDL test bench code, with generated test and output data.

**Note** If you generated Verilog test bench code, the generated file is HDL DUT tb.v.

- HDL\_DUT\_tb\_pkg.vhd: Package file for VHDL test bench code. This file is not generated if you specified Verilog as the target language.

- HDL\_DUT\_tb\_compile.do: Mentor Graphics ModelSim compilation script (vcom commands). This script compiles and loads the entity to be tested (HDL\_DUT.vhd) and the test bench code (HDL\_DUT\_tb.vhd).

- HDL\_DUT\_tb\_sim.do: Mentor Graphics ModelSim script to initialize the simulator, set up wave window signal displays, and run a simulation.

- 3 To view the generated test bench code in the MATLAB Editor, double-click the HDL\_DUT\_tb.vhd or HDL\_DUT\_tb.v file in the Current Folder.

## Run Simulation and Verify Generated HDL Code

To verify the simulation results, you can use the Mentor Graphics ModelSim simulator. Make sure that you have already installed Mentor Graphics ModelSim.

To launch the simulator, use the vsim function. This command shows how to open the simulator by specifying the path to the executable:

```

vsim('vsimdir','C:\Program Files\ModelSim\questasim\10.6b\win64\vsim.exe')

```

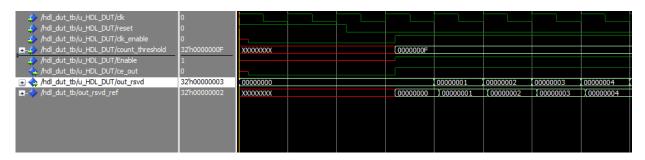

To compile and run a simulation of the generated model and test bench code, use the scripts that are generated by HDL Coder. Following example illustrates the commands that compile and simulate the generated test bench for the hdlcoder simple up counter/HDL DUT Subsystem.

- 1 Open the Mentor Graphics ModelSim software and navigate to the folder that has the generated code files and the scripts.

- 2 Use the generated compilation script to compile and load the generated model and text bench code. For example, if you generated a test bench for the hdlcoder\_simple\_up\_counter/HDL\_DUT Subsystem, run this command to compile the generated code.

```

QuestaSim>do HDL_DUT_tb_compile.do

```

3 Use the generated simulation script to execute the simulation. The following listing shows the command and responses. You can ignore any warning messages. The test bench termination message indicates that the simulation has run to completion without comparison errors. For example, if you generated a test bench for the hdlcoder\_simple\_up\_counter/HDL\_DUT Subsystem, run this command to simulate the generated code.

```

QuestaSim>do HDL_DUT_tb_sim.do

```

The simulator optimizes your design and displays the results of simulating your HDL design in a **wave** window. if you don't see the simulation results, open the **wave** window. The simulation script displays inputs and outputs in the model including the clock, reset, and clock enable signals in the **wave** window.

You can now view the signals and verify that the simulation results match the functionality of your original design. After verifying, close the Mentor Graphics ModelSim simulator, and then close the files that you have opened in the MATLAB Editor.

## **Deploy Generated HDL Code on Target Device**

After you verified the functionality of your HDL design, you can deploy the generated code on a target FPGA device. For deployment, you use the Simulink HDL Workflow Advisor. To learn how more, see "HDL Code Generation and FPGA Synthesis Using Simulink HDL Workflow Advisor" on page 3-39.

# **See Also**

makehdl| makehdltb

## **More About**

- "Test Bench Generation Output"

- "HDL Test Bench"

- "HDL Code Generation and FPGA Synthesis Using Simulink HDL Workflow Advisor" on page 3-39

# HDL Code Generation and FPGA Synthesis Using Simulink HDL Workflow Advisor

#### In this section...

"Simple Up Counter Model" on page 3-39

"About HDL Workflow Advisor" on page 3-40

"Set Up Tool Path" on page 3-40

"Open the HDL Workflow Advisor" on page 3-41

"Generate HDL Code" on page 3-42

"Perform FPGA Synthesis and Analysis" on page 3-43

"Run Workflow at Command Line with a Script" on page 3-44

This example shows how you can use the HDL Workflow Advisor to generate HDL code and synthesize your design on a target Xilinx FPGA. For this tutorial, you can use a simple up counter model that you created as a source for HDL code generation. The model simulates an up counter that counts from zero to a threshold value and then wraps back to zero. To learn how to create this model, see "Create Simulink Model for HDL Code Generation" on page 3-11.

## Simple Up Counter Model

Open this model to see a simple up counter. The model counts up from zero to a threshold value and then wraps back to zero. In this model, the threshold value is set to 15. You can change the threshold value by changing the value of the Constant block that is input to the count\_threshold port. The Enable signal specifies whether the counter should count up or hold the previous value. The Enable signal is set to 1 which means that the counter counts upwards continuously.

```

open_system('hdlcoder_simple_up_counter.slx')

set_param('hdlcoder_simple_up_counter', 'SimulationCommand', 'Update')

```

Note: This model is configured with 'hdlsetup'

Add your design targeted for ASIC/FPGA inside HDL\_DUT and then run the following command: makehdl("HDL\_DUT")

## **About HDL Workflow Advisor**

The HDL Workflow Advisor guides you through the stages of generating HDL code for a Simulink subsystem and the FPGA design process, such as:

- Checking the model for HDL code generation compatibility and automatically fixing incompatible settings.

- Generation of HDL code, a test bench, and scripts to build and run the code and test bench.

- Generation of cosimulation or SystemVerilog DPI test benches and code coverage (requires HDL Verifier).

- Synthesis and timing analysis through integration with third-party synthesis tools.

- Back-annotation of the model with critical path information and other information obtained during synthesis.

- Complete automated workflows for selected FPGA development target devices and the Simulink Real-Time FPGA I/O workflow, including FPGA-in-the-loop simulation.

## Set Up Tool Path

If you do not want to synthesize your design, but want to generate HDL code, you do not have to set the tool path. In the HDL Workflow Advisor, on the **Set Target** > **Set Target**

**Device and Synthesis Tool** step, leave the **Synthesis tool** setting to the default No Synthesis Tool Specified, and then run the workflow.

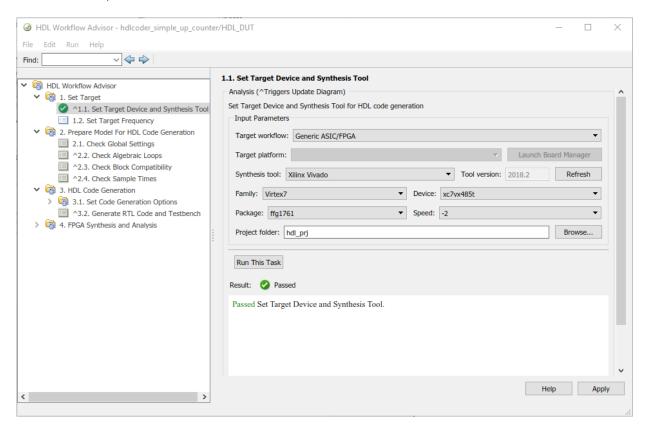

If you want to synthesize your design on a target platform, before you open the HDL Workflow Advisor and run the workflow, set up the path to your Synthesis tool. This example uses Xilinx Vivado, so you must have already installed Xilinx Vivado. To set the tool path, use the hdlsetuptoolpath function to point to an installed Xilinx Vivado 2018.2 executable. To learn about the latest supported tools, see "Supported Third-Party Tools and Hardware" on page 1-3.

```

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',...

'C:\Xilinx\Vivado\2018.2\bin\vivado.bat');

```

**Note** Optionally, you can use a different synthesis tool of your choice and follow this example. To set the path to that synthesis tool, use hdlsetuptoolpath.

## **Open the HDL Workflow Advisor**

To start the HDL Workflow Advisor from a Simulink model,

- 1 In the **Apps** tab, select **HDL Code**. The **HDL Code** tab appears.

- Select the DUT Subsystem in your model, and make sure that this Subsystem name appears in the Code for option. To remember the selection, you can pin this option. Click Workflow Advisor.

When you open the HDL Workflow Advisor, the code generator can warn that the project folder is incompatible. To open the Advisor, select **Remove slprj and continue**.

In the HDL Workflow Advisor, the left pane lists the folders in the hierarchy. Each folder represents a group or category of related tasks. Expanding the folders shows available tasks in each folder. From the left pane, you can select a folder or an individual task. The HDL Workflow Advisor displays information about the selected folder or task in the right pane. The contents of the right pane depends on the selected folder or task. For some tasks, the right pane contains simple controls for running the task and a display area for status messages and other task results. For other tasks that involve setting code or test bench generation parameters, the right pane displays several parameter and option settings.

To learn more about each individual task, right-click that task, and select **What's This?**.

To learn more about the HDL Workflow Advisor window, see "Getting Started with the HDL Workflow Advisor".

## **Generate HDL Code**

In the Set Target > Set Target Device and Synthesis Tool step, for Synthesis tool, select Xilinx Vivado and select Run This Task.

In **Set Target Frequency** task, specify a "Target Frequency" that you want the design to achieve. For this example, you can set **Target Frequency (MHz)** to 200.

3 Leave all settings to default and right-click the Check Sample Times task and select Run to Selected Task.

By running the tasks in the **Prepare Model For HDL Code Generation** folder, the HDL Workflow Advisor checks the model for code generation compatibility.

**Note** If running a task generates a warning, select **Modify All**, and rerun the task.

- 4 To modify code generation options, use the tasks in **Set Code Generation Options**. For example, to customize the target HDL language and the target code generation folder, use the **Set Basic Options** task. After you make changes, click **Apply**.

- 5 To generate code, right-click the **Generate RTL Code and Testbench** task, and select **Run to Selected Task**.

**Note** If you want to generate an HDL test bench or a validation model, you can specify the corresponding settings in the **Generate RTL Code and Testbench** task. To specify additional test bench options, use the **Set Testbench Options** task.

## **Perform FPGA Synthesis and Analysis**

- In the FPGA Synthesis and Analysis > Perform Synthesis and P/R > Perform Place and Route task, clear Skip this task and click Apply.

- 2 Right-click Annotate Model with Synthesis Result and select Run to Selected Task.

- **3** View the annotated critical path in the model.

# Run Workflow at Command Line with a Script

To run the HDL workflow at a command line, you can export the Workflow Advisor settings to a script. To export to script, in the HDL Workflow Advisor window, select **File** > **Export to Script**. In the Export Workflow Configuration dialog box, enter a file name and save the script.

The script is a MATLAB file that you can run from the command line. You can modify the script directly or, import the script into the HDL Workflow Advisor, modify the tasks, and export the updated script. To learn more, see "Run HDL Workflow with a Script".

## See Also

hdladvisor | hdlsetuptoolpath | makehdl

## **More About**

- "Tool Setup" on page 2-2

- "Create Simulink Model for HDL Code Generation" on page 3-11

- "Generate HDL Code from Simulink Model" on page 3-27